| 智能频率计的研究与设计 |

数字频率计与传统纯硬件电路的测量方式相比, 有着成本低, 速度快, 空间占用率低等优点。可以实现量程的自动切换, 对脉冲宽度等其他参数进行测量的功能[1]。

目前主流的数字频率计设计方案有采用小规模数字集成电路制作, 采用FPGA芯片作为控制核心, 采用单片机为主控制芯片等方案[2]。小规模数字集成电路设计可以长期储存且稳定性较高[3], 但电路结构较为复杂且无法通过编程实现功能。FPGA的出现突破了硬件设计方面的体积大、难于集成、设计完后不容易更改的瓶颈[4], 但是价格昂贵且编程复杂。随着单片机技术的发展, 单片机已经可以完美弥补以上缺点, 实现高精度, 快速度, 小体积的频率计设计[5]。基于单片机的数字频率计利用单片机内部的定时/计数器直接计算频率[6], 选用MAX232芯片进行单片机与PC机的电平转换[7], 以此进行测量参数如波形、量程等选择, 这样可以实现多波形、大量程测量, 但操作复杂需要人工干预, 不够方便, 且由于计算方式问题会出现误差[8]。

本设计的大体流程为通过单片机内自带的定时/计数器, 将经过整流、分选频电路[9]后的输入信号在多个不同周期中分别进行测量[10], 从而达到高频率、高精度、低误差的性能指标, 最后将测量频率值输出至LCD1602液晶屏显展示结果, 可以实现多波形测量及量程的智能切换。

1 智能频率计 1.1 概述本课题介绍的以单片机为核心设计的智能数字频率计, 可以测量10 Hz~1 MHz的频率, 测量波形为三角波、矩形波、正弦波。

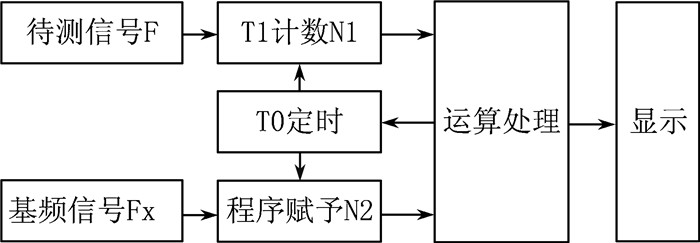

1.2 测量原理本次设计选择了多周期同步测频法。多周期同步测频法是基于传统直接测频法改进而来的。传统的直接测频法是将待测信号输入到单片机计数器的计数输入端, 使计数器在标准时间T内进行计数, 但是由于计数器只能进行整数计数, 所以会有误差。多周期同步测频法是指在闸门时间内分别记录待测信号F和基频信号Fx的下降沿个数N1, N2, 计算方法为: F=Fx·(N1/N2)。

由于基频信号在规定时间内的下降沿个数是一定的, 所以在设计中可以不设计基频电路而在程序中改用事先测量好的固定基频数, 从而简化硬件电路。

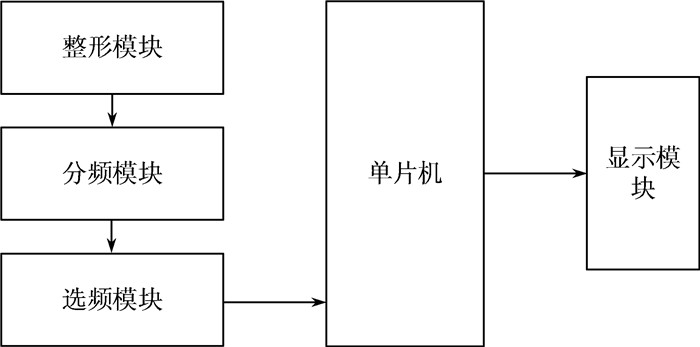

2 系统硬件设计本设计主要由信号整形模块, 分频模块, 选频模块, 显示模块组成。硬件系统框图如图 1所示。

|

| 图 1 硬件系统框图 |

2.1 信号整形模块设计

本次设计所涉及到的三种波形中, 只有矩形波能直接被单片机的输入引脚所识别, 所以如果想测量三角波、正弦波和矩形波, 必须在信号输入端设计一个信号整形模块以实现在信号输入到单片机前, 将除矩形波外其他波形整形成矩形波的功能。要实现将输入信号都转换为可以为单片机识别的方波并进行信号整形、增强其抗干扰能力这个目的, 采用施密特触发器是最常用且简单有效的。

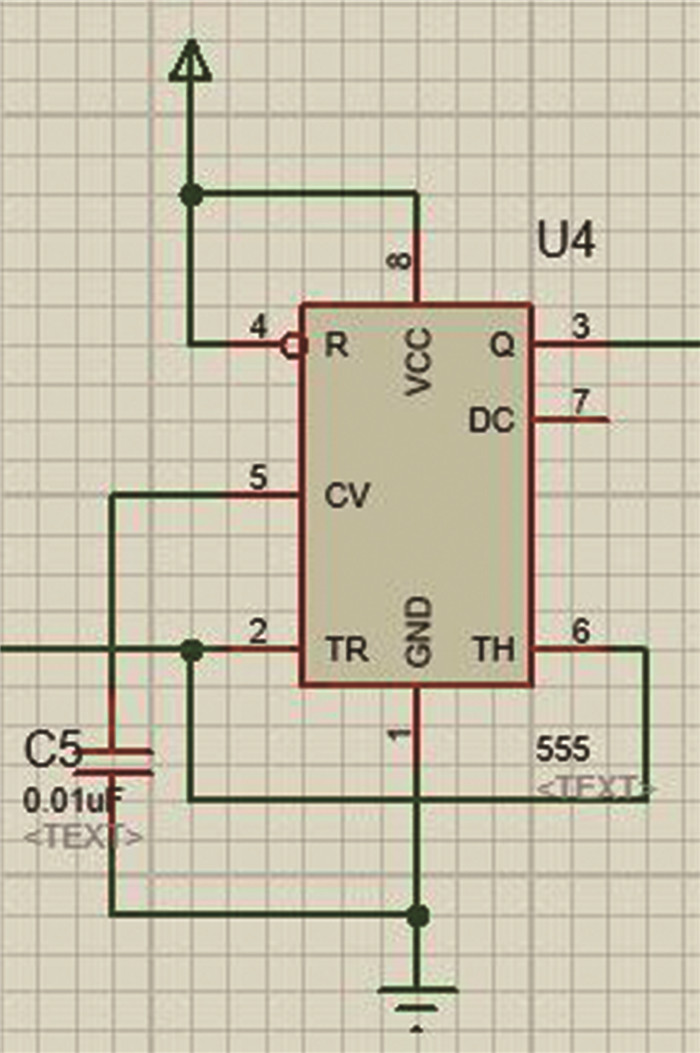

555定时器本身引脚通过一些特殊连接方式加之以简单辅助电路就可以构成一个施密特触发器, 只需将555定时器的阈值输入端与触发输入端共同作为总输入端, 再加以周围一些简单电路就形成了一个施密特触发器。在新构成的施密特触发器中, 1、8管脚分别接地和电源;2、6管脚分别为低触发端TR和高触发端TH, 二者相连后共同连接信号输入端作为信号总输入端;3管脚输出信号的高低电平是由6和2管脚共同接收的电压决定的, 施密特触发器的正负阈值电压分别为2VCC/3和VCC/3。当输入信号一直减小到低于负向阈值时, 3口输出的电压变为高电平;当输入信号增大到高于正向阈值时, 3口输出电压变为低电平。从而实现了将模拟信号波形转变为矩形波的目的。5管脚是一个用来做信号整形防止外部干扰扰乱波形的接口, 本设计中接一个0.01 μF的电容。

以施密特触发器为主体的信号整形模块的硬件电路设计如图 2所示。

|

| 图 2 信号整形电路 |

2.2 分频选频模块设计

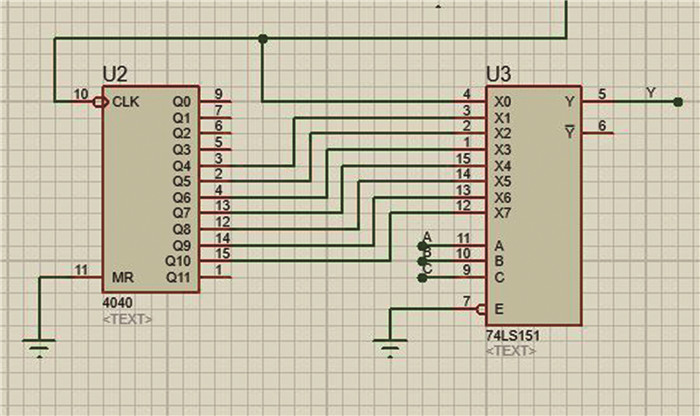

本设计决定用CD4040作为分频模块的分频芯片, 其最大的分频倍数为4 096倍, 足以保证本次设计的要求。经过分频后的信号还需要一个数据选择器来选择具体分频倍数, 最后决定用数据选择器74LS151作为数据选择器, 它可以对数据进行八选一操作。当CD4040的CLK口接收到来自施密特触发器送出的下降沿后开始计时, 信号经过计数器经分频送至计数器脉冲输出端。计数器脉冲输出端与数据选择器的8个输入数据端D0至D7相连接。单片机控制数据选择器根据D0至D7端口上接收到的信号确定一个分频倍数。单片机的P3.2、3.3、3.4接口各自接CD4040中的地址端口A、B、C, 然后通过编写的软件的功能来实现数据的合理化选择, 软件根据分频倍数和计数器计数N1的结合选择一个端口的数据写入单片机。(此处举例74LS151经过地址译码选择数据端时的情况: 若ABC=000, 则向输出端写入D0口的数据;若ABC=111, 则向输出端写入D7口的数据)

分频控制模块电路图如图 3所示。

|

| 图 3 分频选频控制模块 |

2.3 单片机内部的定时器/计数器

本次设计的完成就是依赖于单片机内部的定时/计数器。在智能频率计中首先将单片机中工作方式寄存器的M1口置0, M0口置1, 让内部定时/计数器作为16位定时/计数器工作, 即工作方式1。然后设置T0为定时器, T1为计数器, 即令控制T0的C/T口置0, T1的口置1。

安排好他们两个的工作方式和功能后, 通过软件给与定时器T0赋予600 ms闸门时间并通过TR0、TR1启动定时器计数器, 由于本次设计采用的是多周期同步测频法, 所以除被测信号外还要知道基频信号, 但是由于基频信号频率一定, 本着简化电路的原则就不在此设计中使用定时器T2测量基频信号而是由程序中直接给出。这样只需让T1计数得出被测信号N1, N1是由单片机的P3.5引脚上的高低电平信号中下降沿个数决定的。在此时, 分频倍数也通过程序辅助选好, 即当单片机P3.5口从选频模块选择时, 先从数据选择器的D7口进行选择, 在数据选择器上的每个口都有对应的N1的范围, 当N1范围不在D7口时, 地址自动加1, 从D6口进行选择, 以此类推直到选择到合适的分频倍数。一切确定后将N1、N2送入单片机中的运算处理单元进行计算。

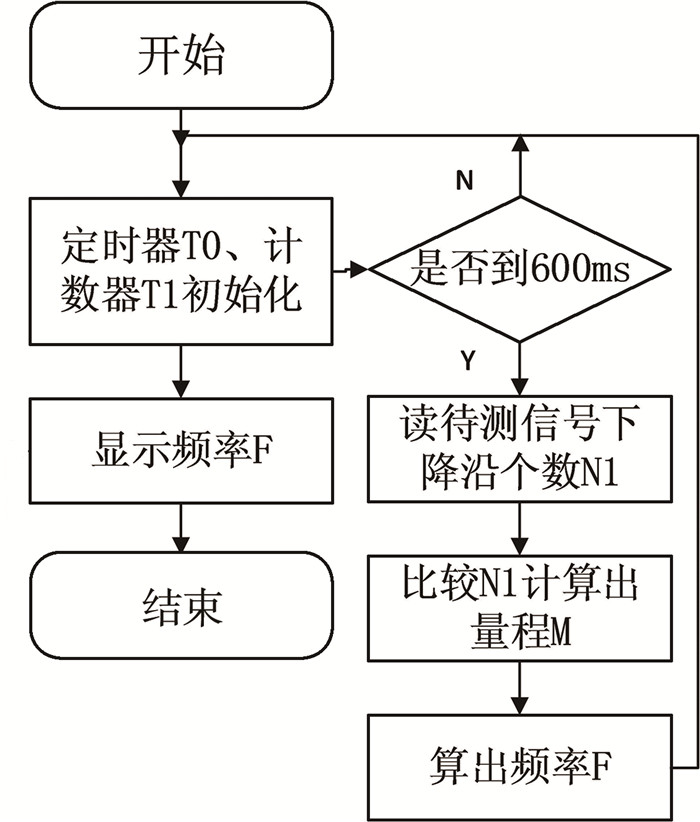

此过程大体流程图如图 4所示:

|

| 图 4 定时/计数器工作流程 |

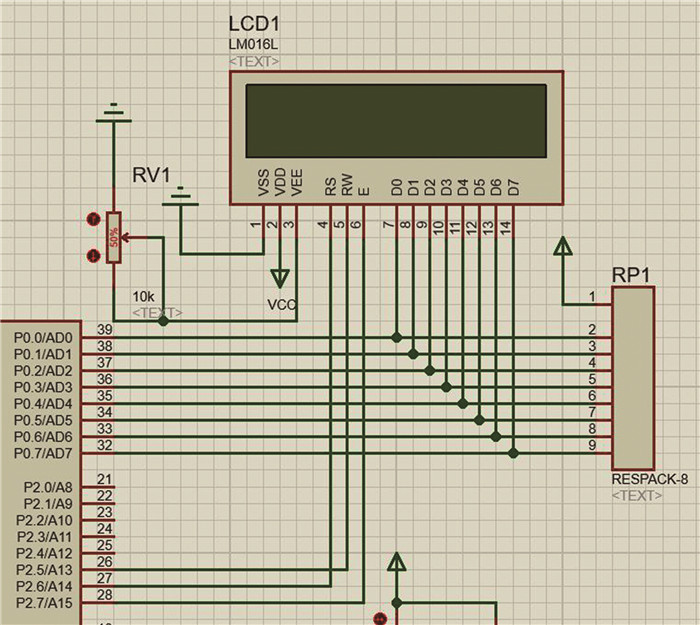

2.4 显示电路模块设计

LCD1602的1脚2脚分别接地和电源, 3脚为液晶显示器对比度调整端, 接正电源时对比度最弱, 接地时对比度最高, 对比度过高时会产生“鬼影”, 使用时通过一个10 K的滑动变阻器调节电压从而调节对比度。在整个芯片中控制该模块执行指令的引脚为6引脚, 当该引脚上电平发生由高到低的跳变时, 该模块开始工作。显示模块电路原理如图 5所示。

|

| 图 5 显示电路 |

3 系统软件设计

一个设计如果想实现其目标功能, 只靠硬件电路是不够的, 还需要软件电路的“驱动”。

当程序开始运行后, 首先打开定时器中断, 然后通过编程实现对定时/计数器T0、T1的工作模式进行定义。令T0用于定时, 周期为600 ms, T1用于记数, 对LCD1602进行初始化, 并写入初始显示内容, 将分频倍数与频率拆分后, 逐个写入显示屏进行显示。主程序流程图如图 6所示。

|

| 图 6 主程序流程图 |

中断开始后, 先对原程序进行入栈/压栈处理, 然后用N1记录定时器T1的值(定义一个16位的变量, 先接受高8位数据, 左移8位后再接受低8位数据), 用N1计算出计数频率, 再根据N1选择分频倍数, 之后计算出测量频率, 将定时器T0, 计数器T1重置后, 对原程序进行出栈, 中断结束。

LCD显示时, 首先将LCD初始化。在程序中0代表第一行, 1代表第二行, 向0写入“fenpin: ”, 向1写入“Fre: Hz”。然后读LCD忙状态子程序, 先将数据口P0全部设置为高电平, 通过为引脚赋不同值进行读命令, LCD1602忙信号在D7口, 检测D7口状态若为1则忙碌, 此时输入信号会被无视, 需要等待, 当其不忙后向LCD写命令或数据。

本设计可以检测8位数值, 首先显示第8位上的数字, 测量的频率对10 000 000取整后再对10取余即为最后显示数值第八位上的数字, 同理第7位上的数字是测量的频率对1 000 000取整后再对10取余, 以此类推显示出8位频率。然后对分频倍数进行显示, 方法与频率显示一样只不过分频倍数只有4位。

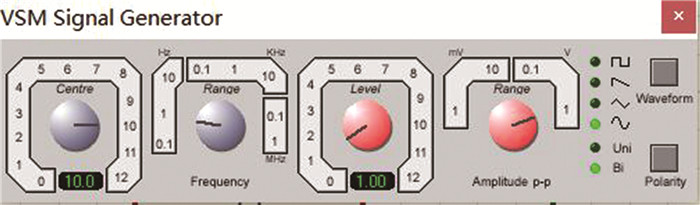

4 系统仿真 4.1 系统仿真仿真前, 因为要验证该设计是否能测量多种波形所以要先在本次设计的信号输入端加一个Proteus函数发生器, 正极接频率计的信号输入端, 负极接地。进行仿真,随后弹出函数发生器设置面板, 其中Frequency的作用是调节频率、Amplitude的作用是调节幅度、Waveform的作用是波形切换、Polarity的作用是单双极性切换、Range为选择量程。如图 7所示提供正弦波、三角波以及方波的波形选择。

|

| 图 7 函数发生器控制面板 |

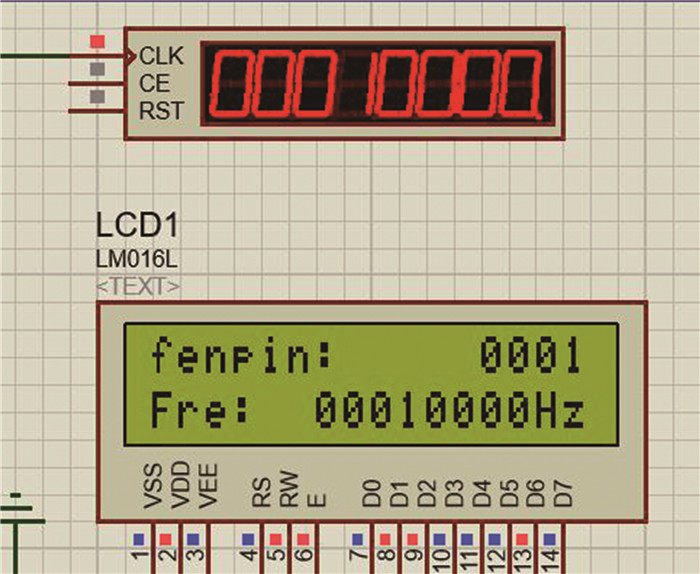

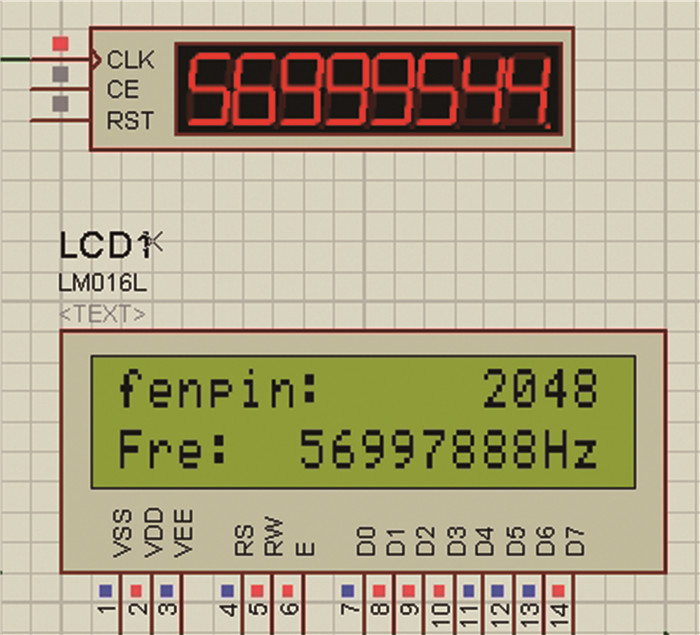

随便输入频率值与波形后, 频率计显示出数字, 直接与信号输入端口连接的数码管所显示数字为实际输入信号的频率值, 而LCD液晶显示屏显示的则是本次仿真通过整形、计算、LCD计算后的测量频率。LCD屏第一行为分频倍数, 从2 048开始向下减直到选择到合适的分频倍数, 第二行是测量值它随着分频倍数的变化发生变化, 当分频倍数确定后, 测量值也随之确定。

本小节以正弦波为例进行仿真验证, 当选择输入频率为低频1 kHz时, LCD显示结果如图 8所示, 此时分频倍数为1。

|

| 图 8 低频信号测量 |

为了证明可以测频率非常高, 随机输入一个很大的数, 此时由于LCD计算和单片机内部定时计数器的计算, 显示时间可能会长一点, 高频段测量结果如图 9所示, 此时分频倍数为2 048, 可以看出此时测量频率和实际频率还是有一定误差的, 造成误差的原因有很多, 下面将会进行讨论。

|

| 图 9 高频信号测量 |

4.2 误差分析

出现误差的原因有两个, 第一测量待测信号的周期个数时由于计算闸门时间的不稳定性导致;第二是由于该设计中存在分频电路, 当分频倍数达到2 048时, 送给单片机T1口计数的下降沿个数会增加一个, 从而导致测量频率误差就会增加2 048。

5 结论本设计采用了当下最为常用的单片机作为硬件核心, 弥补了传统硬件电路造价高, 电路复杂的缺点, 以最小的空间、最简单的电路和最低的造价对各种波形信号的频率进行测量, 采用了多周期同步测频法, 只要周期足够大, 不存在测量死区问题, 测量的准确度得到提升。

采用的12 MHz晶振的单片机理论上存在500 KHz的计数频率上限值, 本设计采用分频模块将高频信号分频, 大大提高数字频率计的量程。分频后采用数据选择器与单片机相连, 通过软硬件结合的方式实现量程的自动切换, 改善了传统频率计需要手动切换量程的特点。

实验证明仿真器件数学模型因为考虑了芯片处理延时, 所以在测高频信号时等待结果的周期比较长。

| [1] |

李建波. 基于单片机和测频法的频率计设计及proteus仿真[J]. 电脑知识与技术, 2018, 14(35): 226-227. |

| [2] |

宋璐. 基于单片机的数字频率计的设计和仿真[J]. 电子设计工程, 2017, 25(1): 140-142, 147. |

| [3] |

徐琛玥. 数字集成电路测试技术应用分析[J]. 集成电路应用, 2020, 37(9): 8-9. |

| [4] |

姜志健. 基于FPGA的高精度频率计的设计与实现[J]. 电子测量技术, 2017, 40(5): 41-46. |

| [5] |

樊利军. 基于单片机的智能数字频率计的设计与实现[J]. 北京工业职业技术学院学报, 2012, 11(3): 32-35. |

| [6] |

赵银铃. 基于单片机的数字频率计的设计与实现[J]. 电子设计工程, 2017, 25(18): 178-180, 184. |

| [7] |

杨春兰. 基于单片机的多功能数字频率计的设计[J]. 怀化学院学报, 2016, 35(5): 64-67. |

| [8] |

廖磊. 一种多周期同步测频的改进方法及误差分析[J]. 乐山师范学院学报, 2011, 26(12): 15-17. |

| [9] |

王捷, 艾红. 数字频率计分频电路的设计[J]. 计算机测量与控制, 2003(2): 156-157, 160. |

| [10] |

应朝龙. 基于单片机的实用数字信号源与频率计设计[J]. 电子设计工程, 2015, 23(20): 141-143, 147. |

2021, Vol. 35

2021, Vol. 35